Arm Gic Tutorial

The Arm On Demand Online Training platform has been designed to give you access to online videos assessment and document based training when and where you want it. The platform contains training modules covering a wide range of topic from AMBA bus protocols to DynamIQ and Armv8-A.

Arm Gic 6 Gicv3 Architecture Lpi Programmer Sought

Bare-metal C programming on ARM.

Arm gic tutorial. USING THE ARM GENERIC INTERRUPT CONTROLLER For Quartus II 140 2ARM Generic Interrupt Controller As illustrated in Figure1 the ARM generic interrupt controller GIC is a part of the ARM A9 MPCORE proces-sor. From the ARMGIC specifications we can see that the programming required to generate LPIs on a bare-metal framework is considerably more than the programming required for the other 3 types. The GIC is connected to the IRQ interrupt signals of all IO peripheral devices that are capable of generating interrupts.

You can explore the repository or read things in order. How does mbed and the rtos handle device interrupts through GIC. GIC architecture splits logically into a.

In keeping with this tutorial series lets not get bogged down with trying to over-complicate a driver. All we want to do is configure this peripheral from its reset state to send all interrupts to CPU0. Arm is only willing to license the.

Further information available as ARM spec GIC Arch 20 and GIC Arch 30 40 148 is the interrupt number IRQ_TYPE_LEVEL_HIGH is the interrupt flag detailed in the documentation. More specifically it deals with a ARMv7A version of the ARM Versatile Express platform emulated on a regular PC through QEMU. The GIC is connected to the IRQ interrupt signals of all IO peripheral devices that are capable of generating interrupts.

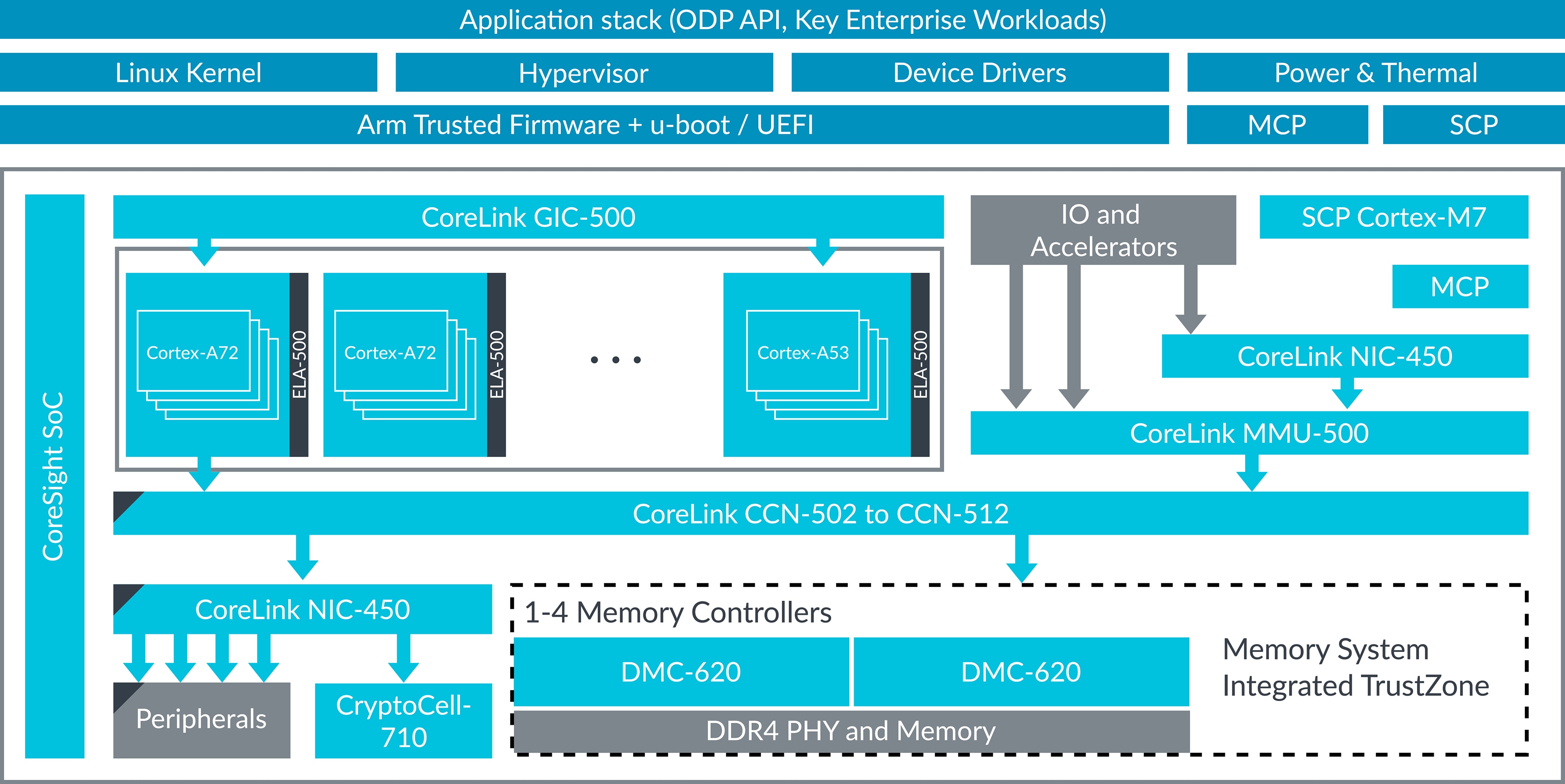

The GIC-500 only supports Arm v80-A cores that implement the GIC CPU interface with the Standard GIC Stream Protocol interface such as Cortex-A72 Cortex-A57 and Cortex-A53. The Arm GIC architecture has two forms in general use with the A-profile that are also applicable to the R-profile. Interpret transactions being issued by the Arm GIC of choice GIC-500 GIC-600 GIC-600AE GIC-625 or GIC-700 in the system.

GICv2 is a memory mapped solution supporting up to eight processors. Interrupt Controller GIC featured by ARM Cortex-A9 MCUs the hard processor system HPS integrated in Altera Cyclone V SoC devices. USING THE ARM GENERIC INTERRUPT CONTROLLER For Quartus Prime 151 2ARM Generic Interrupt Controller As illustrated in Figure1 the ARM generic interrupt controller GIC is a part of the ARM A9 MPCORE proces-sor.

I have read the Renesas reference manual the Arm GIC manual and several online tutorials on using the interrupt controller but I cant quite figure out if mbed provides an interrupt handler on the A9 core or if I have to provide one in my code. The GIC-500 receives message-based interrupts as writes to the AXI4 slave interface or other interrupts from physical inputs. The GIC is a centralized resource for supporting and managing interrupts in a system that includes at least one processor.

Arm generic interrupt controller gic architecture specification licence this end user licence agreement licence is a legal agreement between you either a single individual or single legal entity and arm limited arm for the use of the relevant gic architecture specification accompanying this licence. There is also the ARM GIC Architecture documentation to consider too. Then in section 2 it quickly discusses.

The ARM GIC is primarily used in the Cortex-A MPCore series processors but it not specific to any processor. Documentation There is GIC-400 documentation available from ARM. This post is not intended to be standalone guide to triggering LPIs.

There is GIC-400 documentation available from ARM. The ARM GIC is part of the ARM processor private bus interface. 4 years 11 months ago.

It can ideally be used to form a clear high-level picture of the programming needed. Exceptions Exception Level virtualization A basic knowledge of the AXIACE protocol. If necessary the class can be extended to cover these.

A basic knowledge of some Arm architecture concepts eg. This repository contains a tutorial ebook concerning programming a bare-metal ARM system. ARMv8-A CPU Architecture Overview Chris Shore ARM Game Developer Day London Training Manager ARM 03122015.

Also we should mention that if the touchscreen interrupt passes through another Interrupt Controller before getting to GIC then we actually change the CPU affinity of all the interrupts handled by that Interrupt Controller. In keeping with this tutorial series lets not get bogged down with trying to over-complicate a driver. There is also the ARM GIC Architecture documentation to consider too.

All we want to do is configure this peripheral from its reset state to send all interrupts to CPU0. GICv3 offers support for much higher interrupt counts and larger numbers of processors. Still interrupt load on the newly assigned CPU core will.

However the ARM GIC only supports one CPU core per interrupt.

Generic Interrupt Controllers Arm Developer

Arm Gic 6 Gicv3 Architecture Lpi Programmer Sought

Generic Interrupt Controllers Arm Developer