Dma Controller Tutorial

8257 dma controller. As its name says DMA does data transfers between memory locations without the need for a CPU.

Stm32 Dma Tutorial Using Direct Memory Access Dma In Stm32

Using DMA instead actually required.

Dma controller tutorial. We use the LED library from the previous tutorial they indicate a start and stop-transfer for both modes DMA and CPU. And it may have DMA controller 1 DMA controller 2 DMA controller 3 Ethernet controller USB controller as Masters. To avoid occupying the CPU most advanced microcontrollers have a Direct Memory Access DMA controller.

A o - A 3. The DMA Controller also has supporting 24-bit registers available to all the DMA. Each DMA channel has one DCR.

Direct Access Media DMA. Hence it turns out to be 19μs per byte. It is a clock frequency signal which is required for the internal operation of 8257.

When an IO port needs DMA service activation of the DRQ input of a channel. You program the DMA controller using byte addresses. These are the four least significant address lines.

In the programmed data transfer process where we need 766μs per byte only the 4 bytes comes out from the hard disk in the same time repeatedly. In the master mode it is used to load the data to the peripheral devices during DMA memory read cycle. STM32 DMA Tutorial Using Direct Memory Access DMA In STM32.

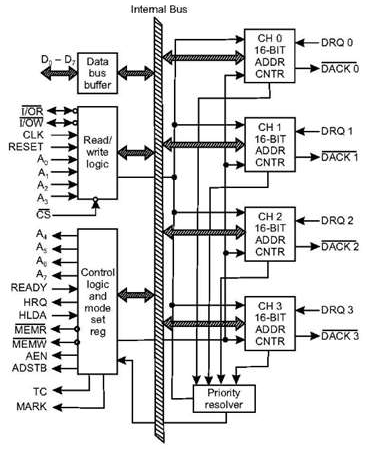

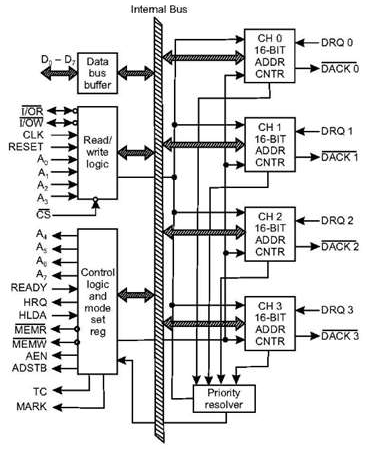

DMA controller contains an address unit for generating addresses and selecting IO device for transfer. As per DIP package Intel 8257 DMA controller chip is a 40-pin programmable Integrated Circuit. The DMA controller reads data from the sour ce address through the master read port and then writes to the destination address through the master write port.

Heres a primer on this most efficient means of moving data around in a system. Read and write start addresses should be aligned to the transfer size. Fig-1 below shows the block diagram of the DMA controller.

In every microcontroller architecture a microcontroller may have multiple masters. DMA in Computer Architecture. As we see in.

In many cases the DMA controller slows the speed of the system when transfers occur. In DMA both CPU and DMA controller have access to main memory via a shared system bus having data address. The DMA controller performs direct memory transfer by sharing the system bus with the Cortex-M3 core.

DMA controller was designed by Intel to have the fastest data transfer rate with less processor utilization. Implementing direct memory access is straightforward once you know how it works and how to configure your DMA controller. Likely the processor also works in two modes namely active mode and HOLD mode.

It specifies the DMA channels which are enabled distinguished they are fixed or rotating. This signal is used to RESET the DMA controller by disabling all the DMA channels. The DMA controller chip 8257 works in two modes namely.

DMA or Direct Memory Access Controller is an external device that controls the transfer of data between IO device and memory without the involvement of the processorIt holds the ability to directly access the main memory for read or write operation. So there will be at least one master that is the processor itself. DMA controller needs the same old circuits of an interface to communicate with the CPU and InputOutput devices.

The function above enables the DMA controller 2 according to the STM32F410RB documentation DMA1 cannot be used for memory-to-memory transfers and performs a single memory-to-memory transfer operation between s_Buffer1 and s_Buffer2. DCR0 DCR1 DCR2 DCR3 DCR4 and DCR5. The DMA controller provides memory with its address and the controller signal selects the IO device during the transfer.

IO devices are connected to system bus via a special interference circuit known as DMA Controller. The direct memory access DMA IO technique provides direct access to the memory while the microprocessor is temporarily disabled. Direct memory access DMA is a means of having a peripheral device control a processors memory bus directly.

A readwrite register that controls the operation of a DMA channel. It also contains the control unit and data count for keeping counts of the number of blocks transferred and indicating the direction of transfer of data. The DMA request may stop the CPU access to the system bus for some bus cycles when the CPU and DMA are targeting the same destination memory or peripheral.

DMA Operational Overview Motorola DMA Controller 10-3 DMA Control Register DCR. The pin diagrams of physical and functional are indicated below. Run the new program and step over the function calls in main to obtain the updated timings.

Data transfer speed is determined by speed of the memory device or a DMA controller. For example to transfer data words if the start. DMA Controller is a hardware device that allows IO devices to directly access memory with less participation of the processor.

This is the situation when DMA data transfer becomes compulsory. After that the processor writes to the control port which intel calls as special mode register. Hence it can be concluded that IO devices plays an important role in the DMA data transfer.

Stm32 Dma Tutorial Using Direct Memory Access Dma In Stm32

Stm32 Dma Tutorial Using Direct Memory Access Dma In Stm32

Microprocessor 8257 Dma Controller Tutorialspoint

Direct Access Media Dma Controller In Computer Architecture Geeksforgeeks